Combinatorial Logic Circuits

Combinatorial Logic Circuits

组合逻辑电路

1. 概述

数字系统由数字电路模块构成,可分为两大类:组合逻辑电路、时序逻辑电路

组合逻辑电路的:

定义:

电路任一时刻的输出状态只取决于该时刻各输入状态的组合,而与电路的原状态无关

特点:

功能上无记忆,结构上无反馈

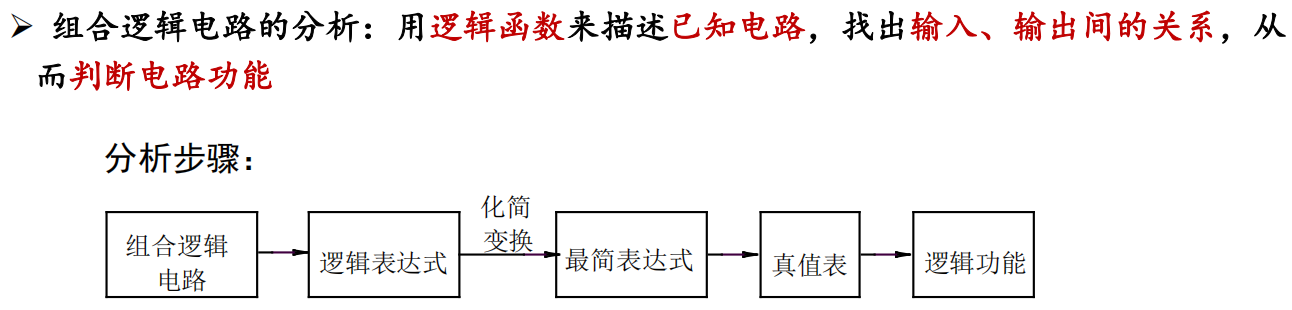

2. 组合逻辑电路的分析

3. 组合逻辑电路的设计

4. 常用的组合逻辑电路

4.1 编码器 译码器

编码器

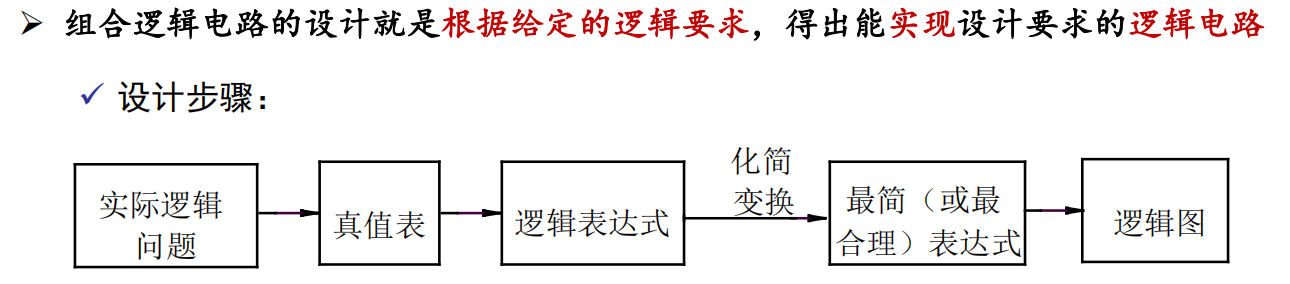

普通编码器

- 对某个输入端出现有效信号的状态进行编码(用二进制表示)

- 任何时刻,只能有一个输入端有有效信号(类似于独热编码)

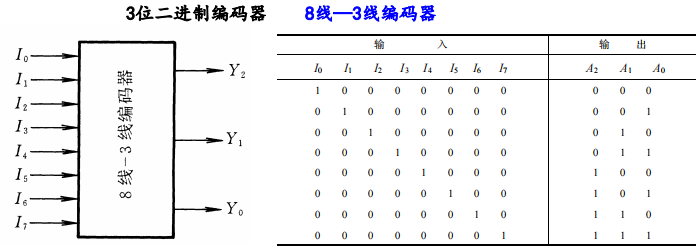

优先编码器

- 允许同时输入两个及以上的有效信号

- 输入信号规定了优先顺序,当有多个有效信号同时出现时,只对优先级最高的信号进行编码。

注:中间那个三角形下半部分全是1

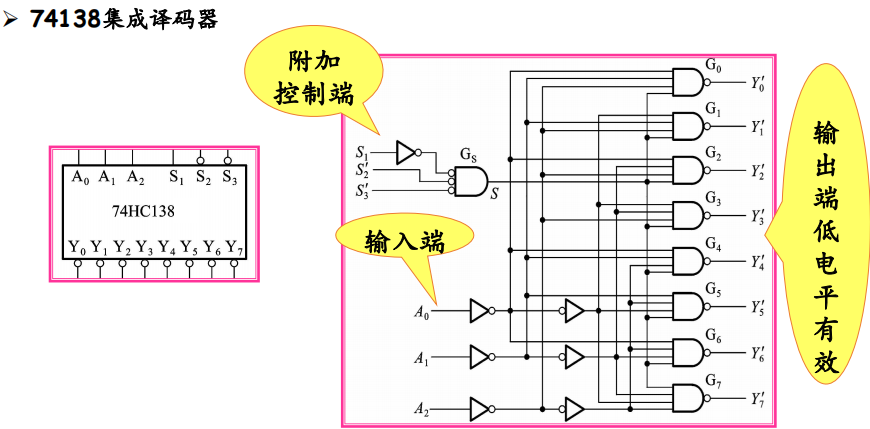

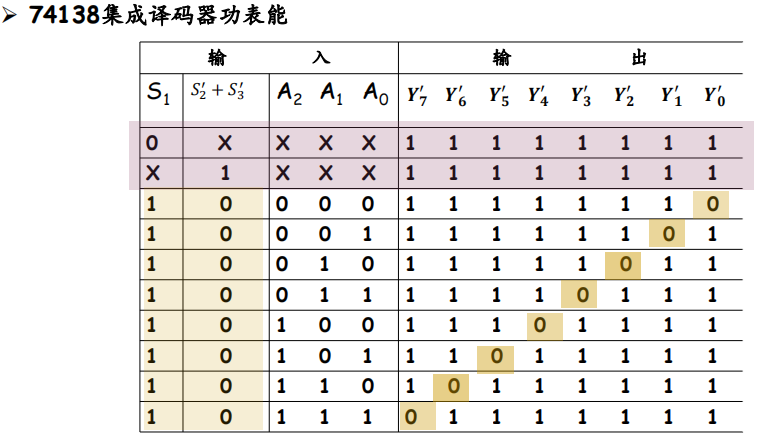

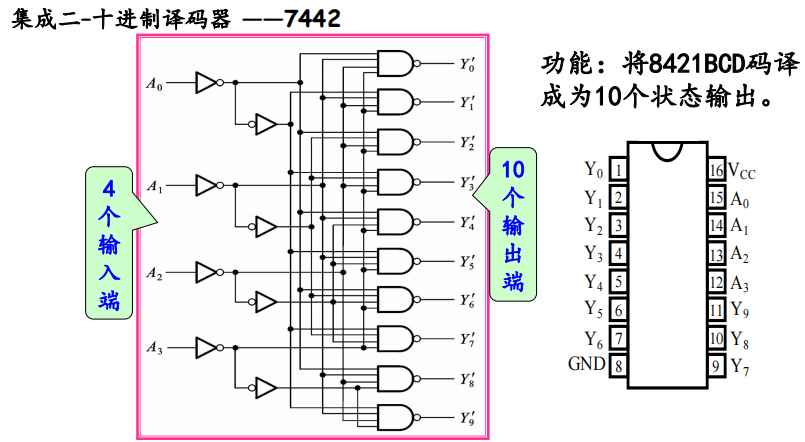

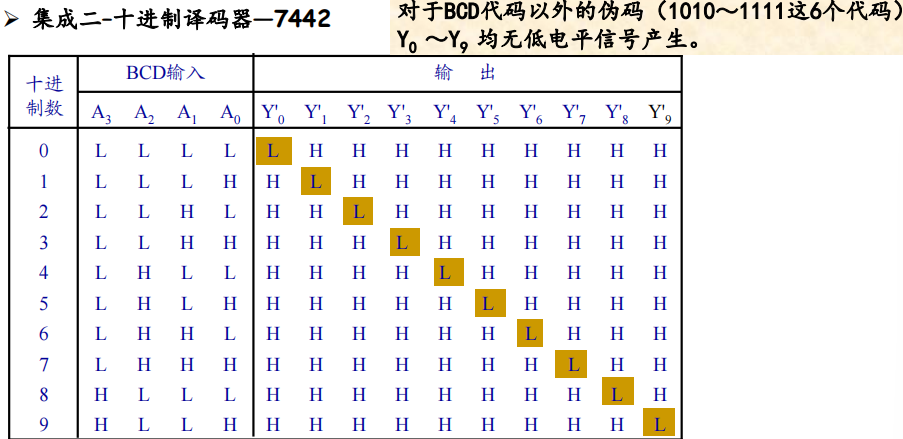

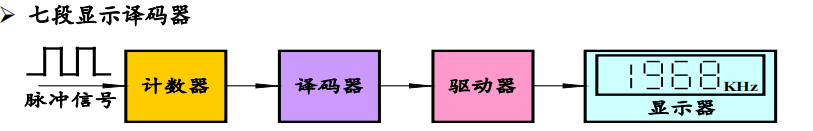

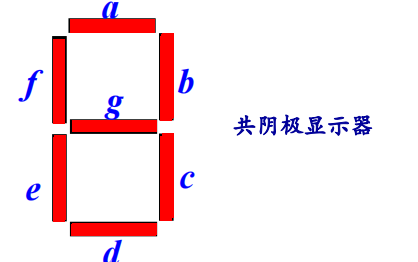

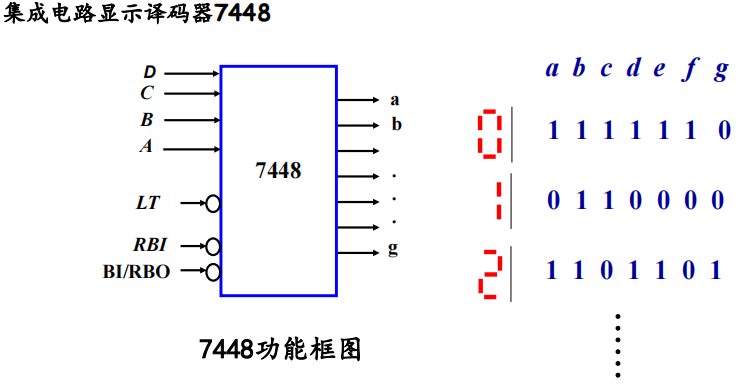

译码器

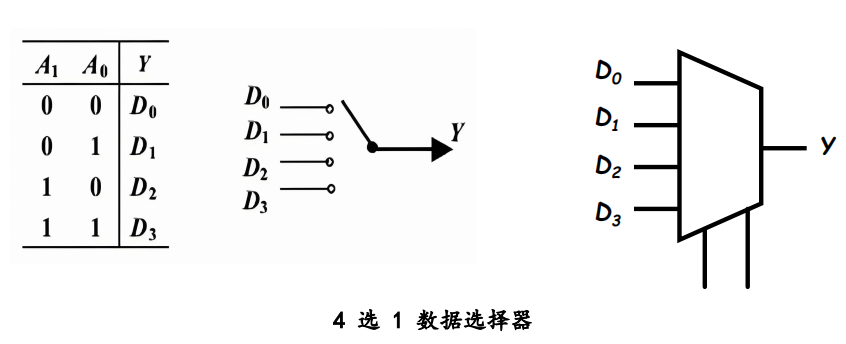

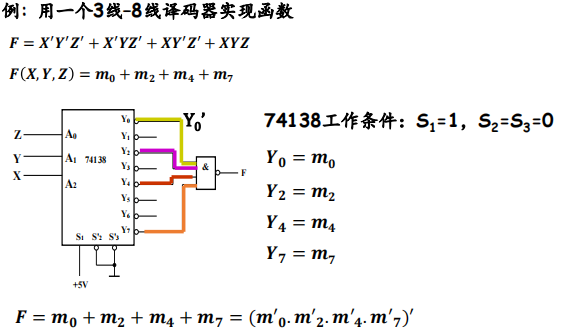

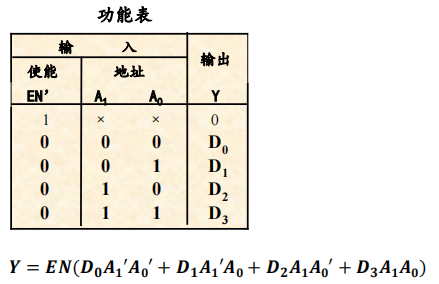

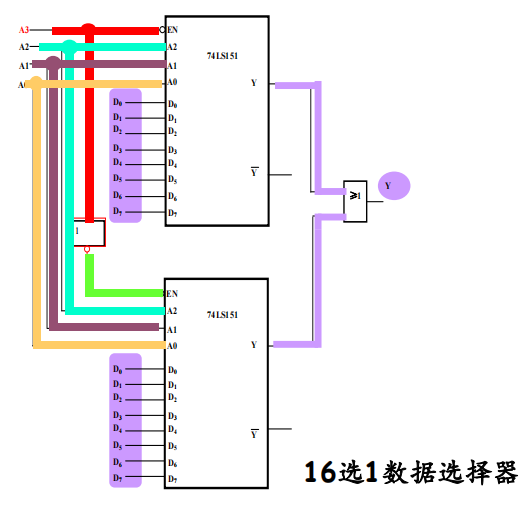

4.2 数据选择器

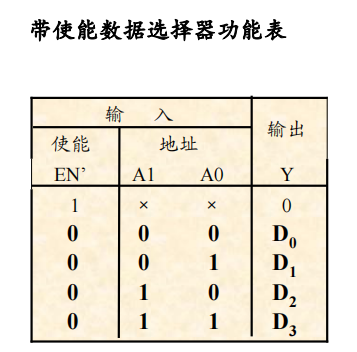

4选1数据选择器

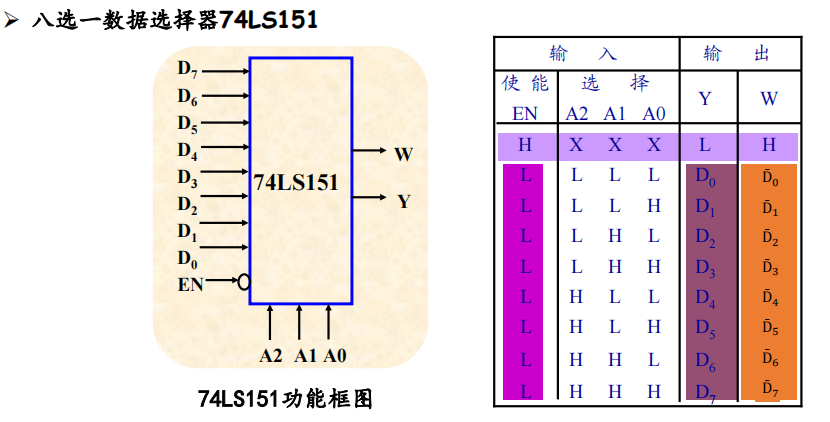

八选一数据选择器

就是通过 $A_2A_1A_0$ 这个二进制数从 $0 \sim 7 $ 中间选一个。让对应编码的 $D_i$ 通路输出到 $Y$ 上,而 $W$ 就是 $\overline{D_i}$

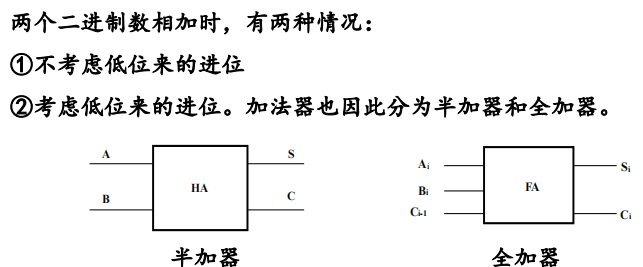

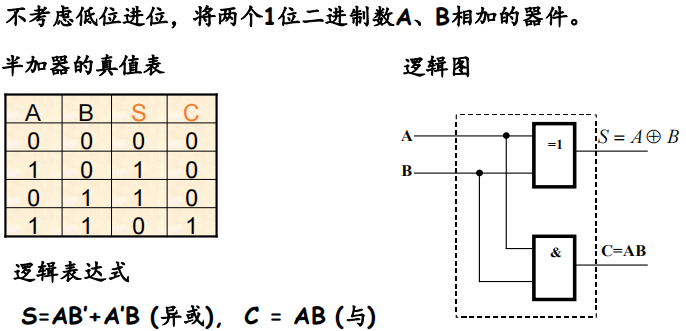

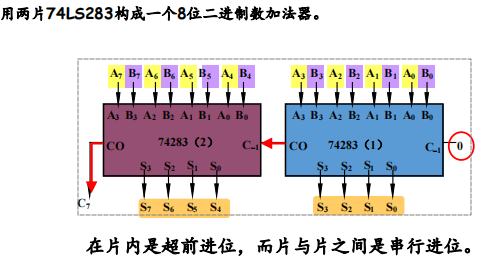

4.3 加法器

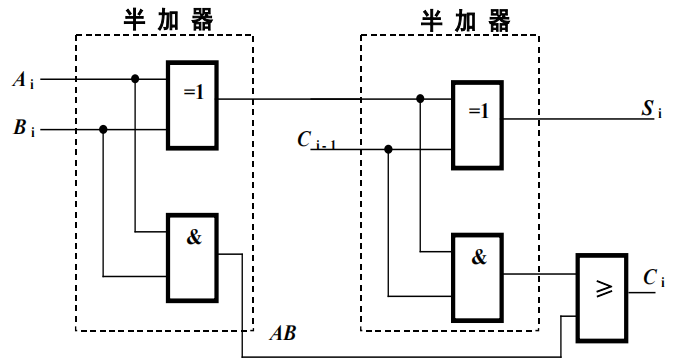

半加器和全加器

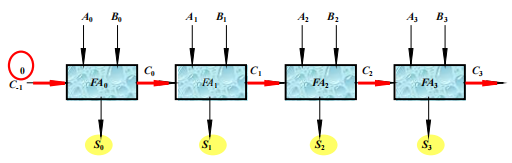

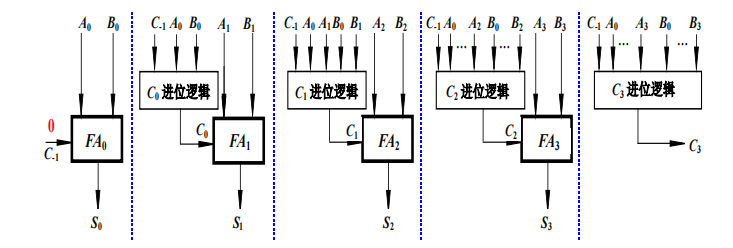

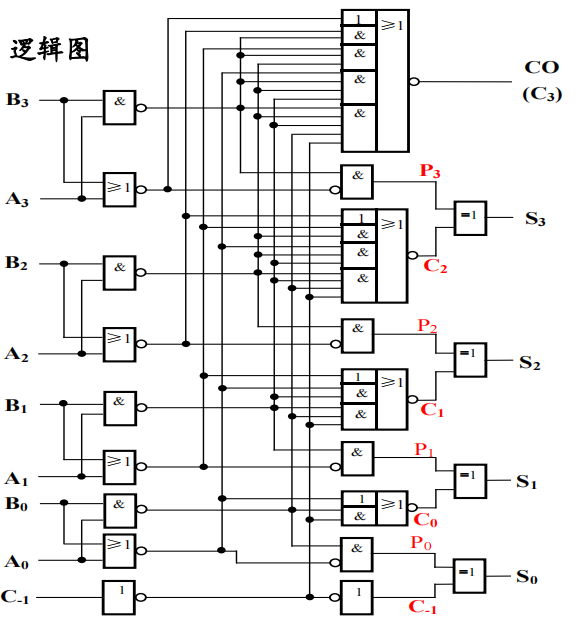

多位数加法器

e.g. 四位二进制相加 $A_3A_2A_1A_0+B_3B_2B_1B_0$

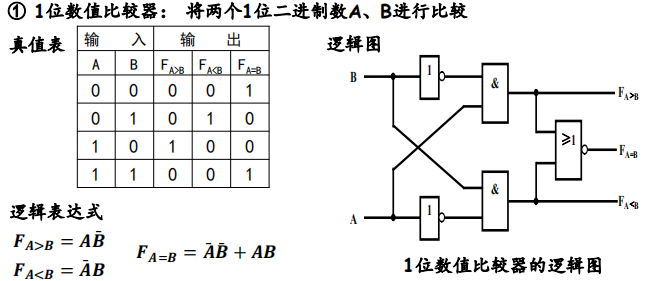

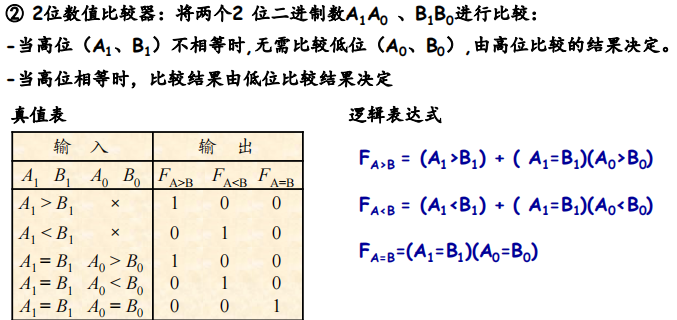

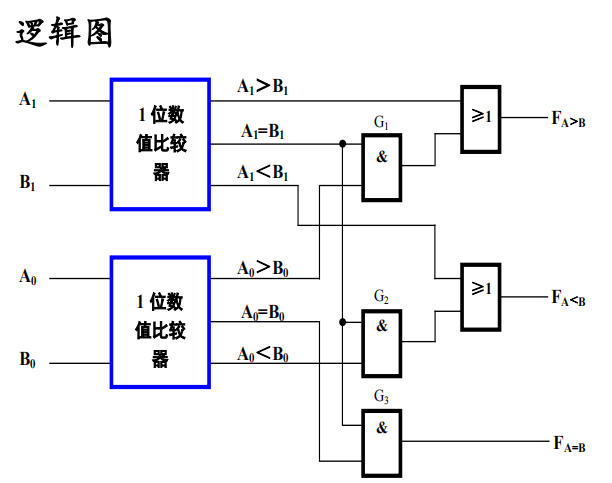

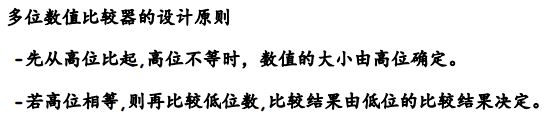

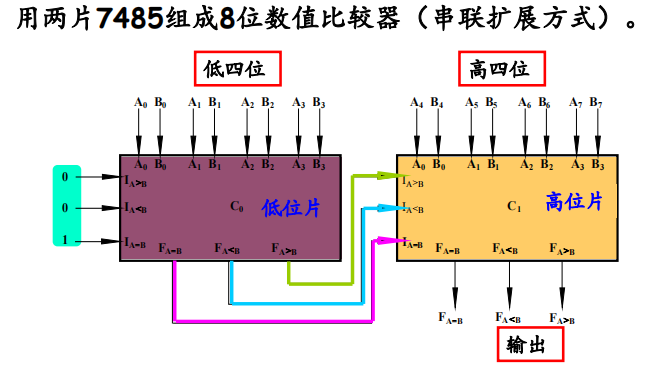

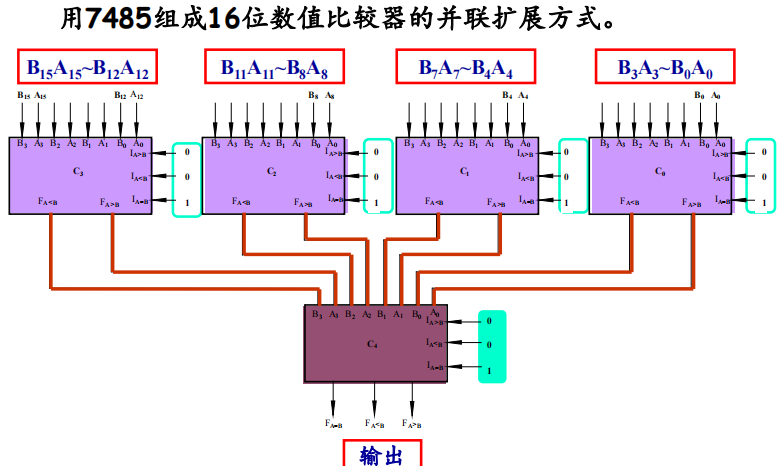

4.4 数值比较器

就是比较两个输入 $A \ B$ 的大小关系的

5. 常用组合逻辑电路的应用

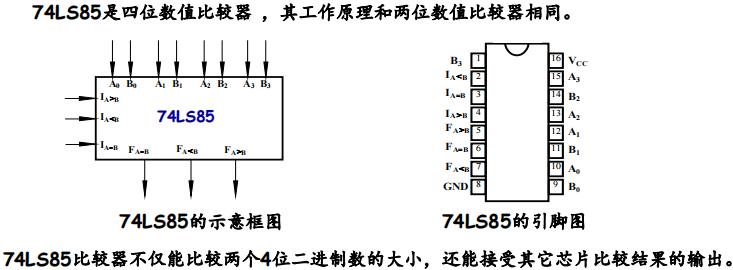

5.1 译码器设计组合逻辑电路

- 省流:很简单,要谁就接上谁,然后用一个“与”门就行。

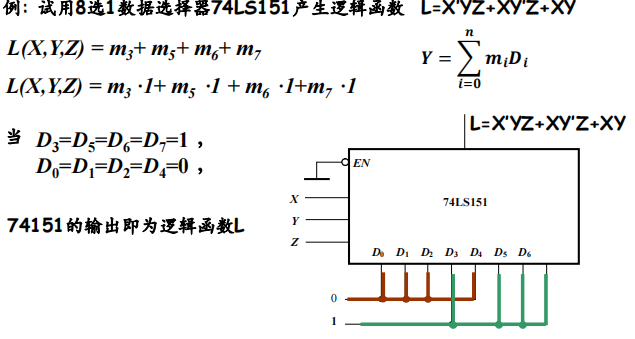

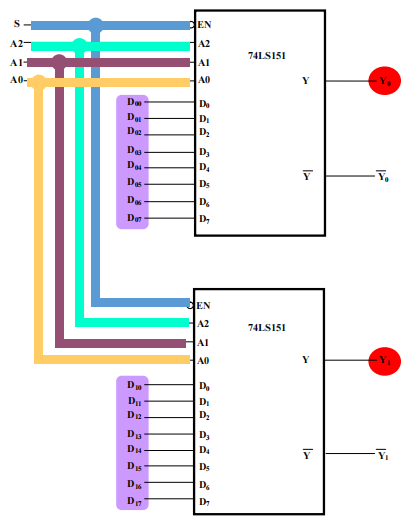

5.2 数据选择器设计组合逻辑电路

- 省流:翻译出对应的数字码,给有的项全接上1,没有的全接上0就行。

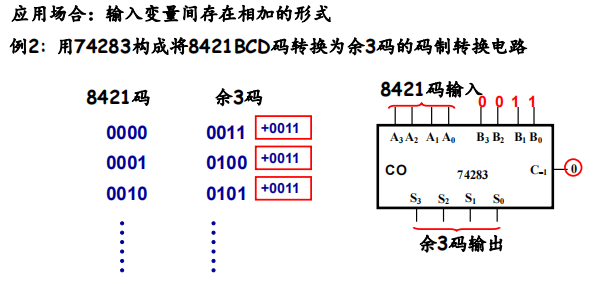

5.3 加法器设计组合逻辑电路

- 省流:想加几就在$B$ 一侧输入几就行了。

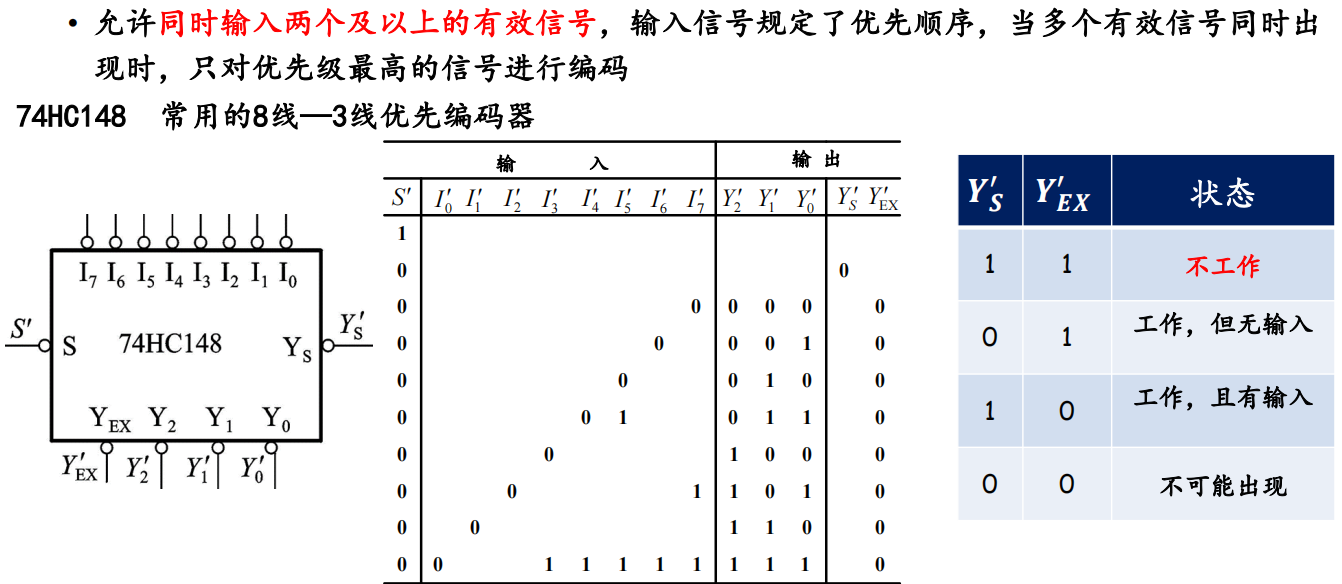

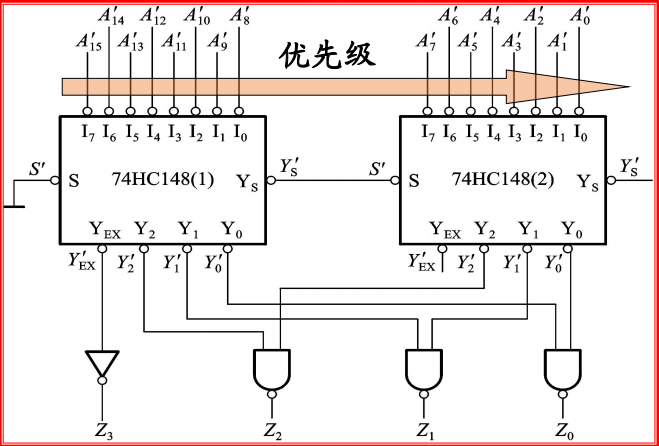

5.4 编码器的扩展

- 16线-4线优先编码器

用2片74HC148 8-3优先编码器接成16线-4线优先编码器

- 为了保证优先级,当第一块有输入时,第二块不能编码,所以将第一块在使能后低电平代表输入的 $Y_S’$ 接入第二块的低电平使能端 $S’$ 即可

- 辨别第一块和第二块,主要在于最高位是不是1,只需要将第一块的 $Y_{EX}^{\prime}$ 取反作为最高位即可

- 后面的3位只需要使用与非门连接,有一个为0(即成功编码)输出位即为1。

5.5 译码器的扩展

5.6 8选1数据选择器的扩展

5.7 数值比较器的扩展

This post is licensed under CC BY 4.0 by the author.